## SENSYLINK Microelectronics

# (CA9512) Level Shifting Hot-swappable f'C-bus and SMBus Bus Buffer

The CA9512 is a hot swappable I<sup>2</sup>C and SMBus buffer. It provides I/O card insertion without corruption of the data and clock buses. It is ideally used in cPCI, VME, Advanced Sensylink cards.

#### 1. Description

The CA9512 is a hot swappable I<sup>2</sup>C and SMBus buffer that allows I/O card insertion into a live backplane without corruption of the data and clock buses and includes two dedicated supply voltage pins to provide level shifting between 3.3V and 5V systems while maintaining the best noise margin for each voltage level. Either pin may be powered with supply voltages ranging from 2.7V to 5.5V with no constraints on which supply voltage is higher. Control circuitry prevents the backplane from being connected to the card until a stop bit or bus idle occurs on the backplane without bus contention on the card. When the connection is made, the CA9512 provides bidirectional buffering, keeping the backplane and card capacitances isolated.

The CA9512 rise time accelerator circuitry allows the use of weaker DC pull-up currents while still meeting rise time requirements. The CA9512 incorporates a digital input pin that enables and disables the rise time accelerators on all four SDAn and SCLn pins.

During insertion, the CA9512 SDAn and SCLn pins are precharged to 1V to minimize the current required to charge the parasitic capacitance of the chip.

The incremental offset design of the CA9512 I/O drivers allows them to be connected to another CA9512 device in series or in parallel and to the I<sup>2</sup>C compliant side of static offset bus buffers, but not to the static offset side of those bus buffers. Available Package: MSOP-8.

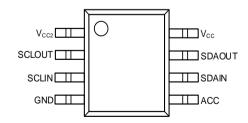

#### 4. PIN Configurations (Top View)

#### 2. Features

- Bidirectional buffer for SDA and SCL lines increases fan-out and prevents SDA and SCL corruption during live board insertion and removal from multipoint backplane systems

- Compatible with I<sup>2</sup>C standard mode, I<sup>2</sup>C fast mode and SMBus standards

- Built-in ΔV/Δt rise time accelerators on all SDA and SCL lines (0.6V threshold) with ability to disable ΔV/Δt rise time accelerator through the ACC pin for lightly loaded systems, requires the bus pull-up voltage and respective supply voltage (Vcc or Vcc2) to be the same

- 5V to 3.3V level translation with optimum noise margin

- High-impedance SDAn and SCLn pins for Vcc or Vcc2 = 0V

- 1V precharge on all SDAn and SCLn pins

- Supports clock stretching and multiple master arbitration and synchronization

- Operating power supply voltage range: 2.7V to 5.5V

- 0Hz to 400kHz clock frequency

#### 3. Applications

- cPCI, VME

- Advanced TCA cards

- Other multipoint backplane cards that are required to be inserted or removed from an operating system

MSOP-8(Package Code MM)

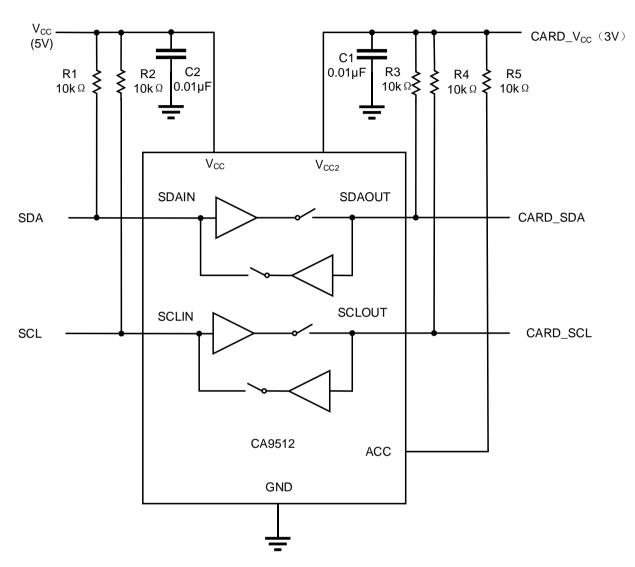

# 5. Typical Application

Figure 1 Typical Application of CA9512

# 6. Pin Description

| PIN Name | PIN No. | Description                                                                                                                                                                                                    |  |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Vcc2     | 1       | Supply voltage for devices on the card I <sup>2</sup> C-bus. Connect pull-up resistors from SDAOUT and SCLOUT to this pin.                                                                                     |  |

| SCLOUT   | 2       | Serial clock output to and from the SCL bus on the card.                                                                                                                                                       |  |

| SCLIN    | 3       | Serial clock input to and from the SCL bus on the backplane.                                                                                                                                                   |  |

| GND      | 4       | Ground supply.                                                                                                                                                                                                 |  |

| ACC      | 5       | CMOS threshold digital input pin that enables and disables the rise time accelerators on all four SDAn and SCLn pins. ACC enables all accelerators when set to $V_{CC2}$ , and turns them off when set to GND. |  |

| SDAIN    | 6       | Serial data input to and from the SDA bus on the backplane.                                                                                                                                                    |  |

| SDAOUT   | 7       | Serial data output to and from the SDA bus on the card.                                                                                                                                                        |  |

| Vcc      | 8       | Supply voltage.                                                                                                                                                                                                |  |

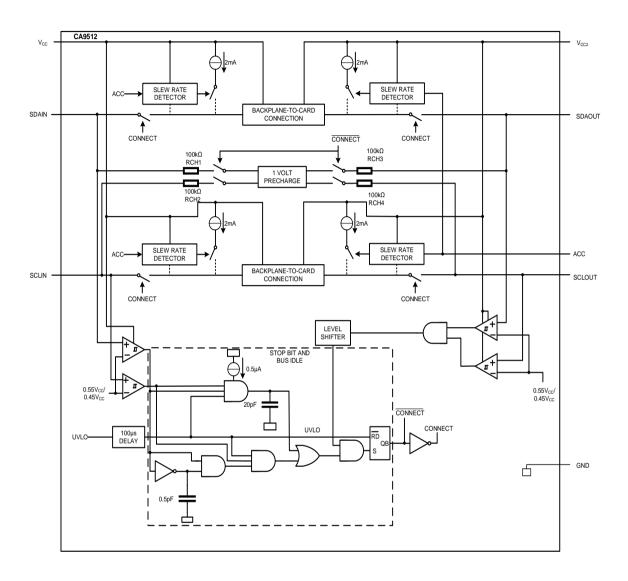

#### 7. Function Block

Figure 2 CA9512 Function block

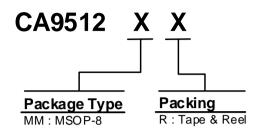

# 8. Ordering Information

| Order PN  | Green <sup>1</sup> | Package | Marking ID <sup>2</sup> | Packing     | MPQ   | Operation Temperature |

|-----------|--------------------|---------|-------------------------|-------------|-------|-----------------------|

| CA9512MMR | Halogen free       | MSOP-8  | 9512<br>YWWAXX          | Tape & Reel | 3,000 | -40°C~+85°C           |

#### Notes:

- 1. Sensylink can meet RoHS2.0/REACH requirement. Most package types Sensylink offers only states halogen free, instead of lead free.

- 2. Marking ID includes 2 rows of characters. In general, the 1st row of characters are part number, and the 2nd row of characters are date code plus production information.

# SENSYLINK Microelectronics Inc.

www.sensylink.com

#### IMPORTANT NOTICE

SENSYLINK Microelectronics Inc. reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein or to discontinue any product or service. Customers should obtain the latest relevant information before placing orders and should verify the latest and complete information. SENSYLINK Microelectronics does not assume any responsibility for use of any product, nor does SENSYLINK Microelectronics any liability arising out of the application or use of this document or any product or circuit described herein. SENSYLINK Microelectronics assumes no liability for applications assistance or the design of Customers' products. Customers are responsible for their products and applications using SENSYLINK Microelectronics components. SENSYLINK Microelectronics does not convey any license under its patent or trademark rights nor the other rights.

SENSYLINK Microelectronics Inc. © 2015 - 2023.